◈ GaN 반도체 이야기--SSPA

https://www.bobaedream.co.kr/view?code=army&No=132105

◈ GaN 반도체 이야기--GaN 용어정리

https://www.bobaedream.co.kr/view?code=army&No=132115

◈ GaN 반도체 이야기--SiC Wafer 1편

https://www.bobaedream.co.kr/view?code=army&No=132130

◈ GaN 반도체 이야기--SiC Wafer 2편

https://www.bobaedream.co.kr/view?code=army&No=132130

요즘 이래저래 바쁘고 정신 없다 보니, 군게도 잘 접속을 못하네요.

오늘은 반도체 8대 공정에 대해 이야기 해보려 합니다.

공정 하나 하나 설명 하려니 분량이 너무 많아, 앞선 이야기들 처럼 쓸데 없는 부분은

다 쳐내고 간단히 설명 하는 정도로.....

그래서 8대 공정에 투입 전 가장 필요한

Epi Wafer 부분을 중점으로 이야기를 풀어 나가려 합니다.

◈ GaN RF 반도체 8대 공정

지금까지는 잉곳에서 웨이퍼까지 단계를 살펴 보았습니다.

아래는 GaN Rf 반도체의 8대공정 흐름도 입니다.

1. 웨이퍼 제조”의 설명을 보면 제작구매 라고 나옵니다.

여기서 웨이퍼 제작,구매는 크게 두가지로 나뉩니다.

가. Bare Wafer :아무런 층이 성장 되지 않은 단순한 베이스판 역할.

나. GaN Epiwafer : Bare Wafer 위에 GaN층이 Epitaxy(성장) 되어 있는 웨이퍼 입니다.

반도체를 제작 하는 회사에 따라, 위의 Wafer 둘 중 하나를 구매 사용하게 됩니다.

반도체 제작 회사에서 직접 Bare Wafer에 Epitaxy 공정을 직접 수행 하게되면,

그 공정은 위 공정도에서 “웨이퍼“와 “산화공정” 사이에 존재 합니다.

Epitaxy이란?

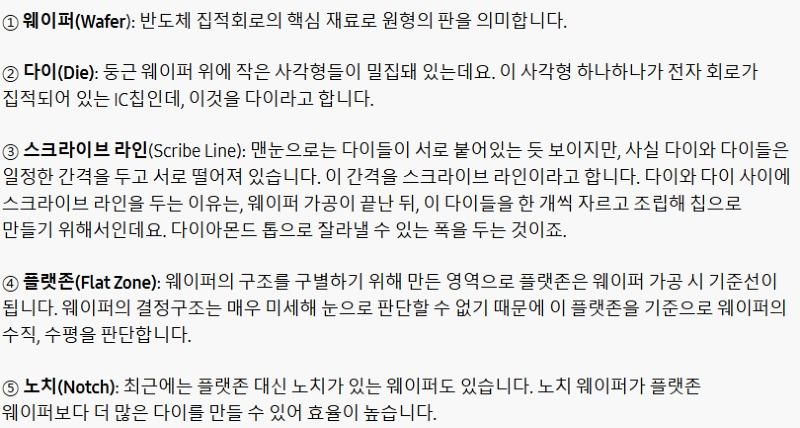

에피(Epi)란 윗 방향으로 더해진다는 뜻이며,

에피택셜(Epitaxial)이란? 윗 축의 방향으로 만들어지는 몸체(Layer)를 뜻 합니다.

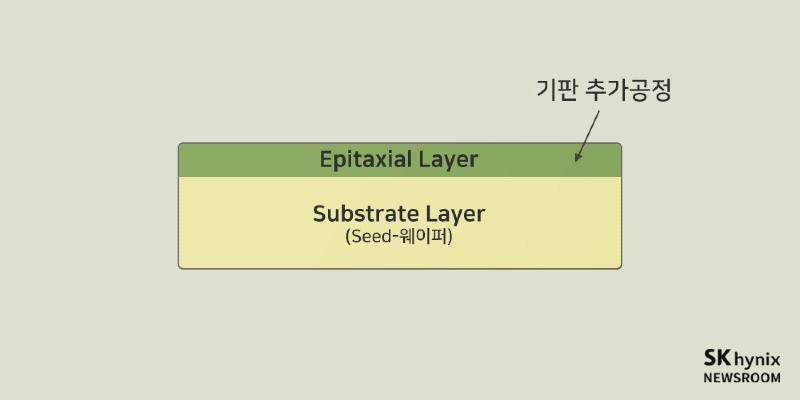

에피택셜 그로스(Epitaxial Growth)는 에피택시(Epitaxy) 혹은 별칭으로

에피(Epi)라고도 부르며, 이는 Seed 웨이퍼를 밑에 깔고 격자 방향을 유지 하면서

단결정(한 종류로 된 결정 전체가 일정한 결정축을 따라 규칙적으로 생성된고체)

으로 성장해 추가로 새로운 층을 쌓아 올린다는 의미입니다.

웨이퍼 표면 위로 반도체 회로의 기본 소자인 트랜지스터(Transistor)를 직접 쌓아 올리기도

하고, 새로운 층을 만들어 이를 기판으로 그 위에 소자를 형성하기도 합니다.

즉 디바이스 특성에 맞춰 여러층을 차례로 쌓아 올리는 작업 이죠.

고객 주문에 따라 또는 공정에 따라 단층 또는 여러층을 쌓기도 합니다.

▶Epi 층 의 주요 요소는 아래 와 같습니다.

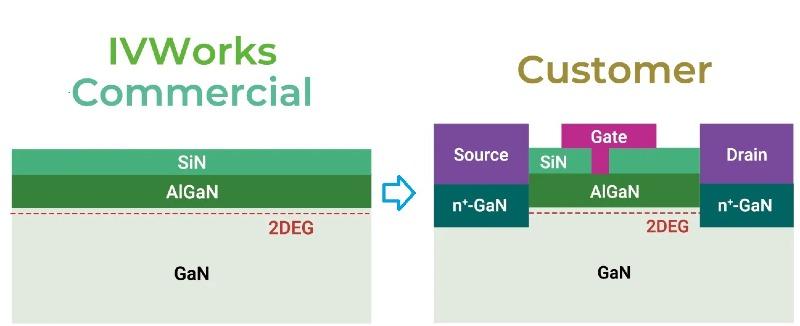

출처 : IVWORKS

1. Stress relaxation layer

에피층에 발생하는 Crack을 방지하기 위한 Stress relaxation 층 성장

2. Semi-insulating layer

전자 소자가 동작할 때 기판 쪽으로 흐르는 누설 전류를 줄여주는 층 성장

3. High quality GaN layer

전자 소자가 동작할 때 전류가 흐르는 통로가 되는 층 성장

4. Heterojunction layer

전자 소자의 구조가 만들어 지는 층 성장

2. GaN On SiC

질화 갈륨은 자연계에 존재는 물질이 아니라서,

갈륨 과 질소를 반응 시켜 GaN 화합물을 만듭니다.

사진 질화갈륨 결정

보통은 MOCVD(Metal-Organic Chemical Vapor Deposition:금속-유기 화학 기상증착)과

MBE (Molecular Beam Epitaxy : 분자선 에피택시)두가지 방법 으로 SiC 웨이퍼 표면에

GaN을 생성 및 성장 하게 됩니다.

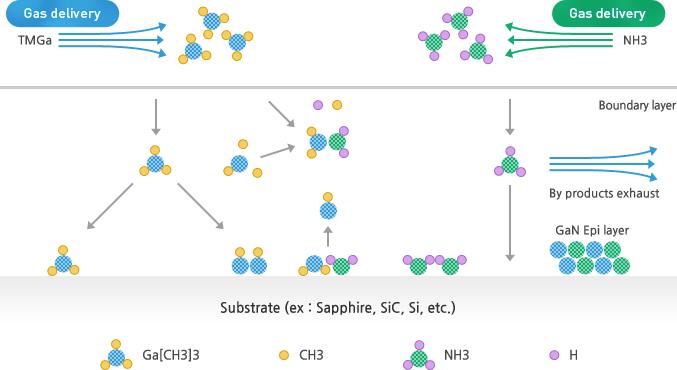

가 .MOCVD

보통은 MOCVD 방식을 많이 적용을 합니다.

고온의 챔버에서 Trimethylgallium (TMGa) + NH₃ (암모니아)가 반응하여,

GaN 박막층을 형성 하게 됩니다.

그림 MOCVD 개략도

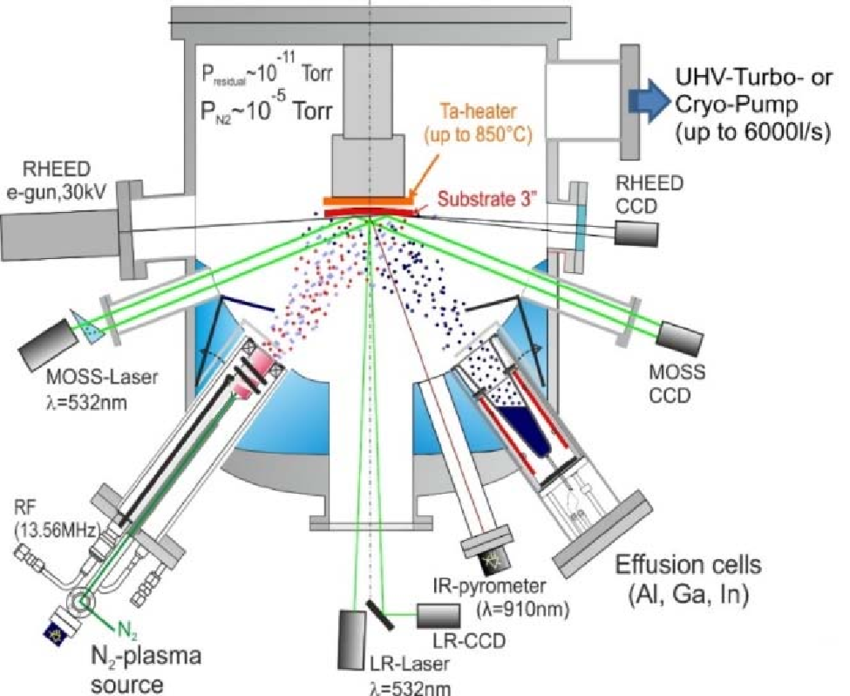

나. MBE

MBE는 초고진공 상태 환경에서 “effusion cell”에서 Ga를 서서히 증발 시켜, GaN 원자가

Molecular Beam을 따라 웨이퍼 위로 유도가 되고, 동시에 쏘아진, 플라즈마화 된 질소를

웨이퍼상에서 만나 질화반응을 유도 Ga원자+활성질소가 반응하여, GaN층을 고르게

성장시키게 됩니다.

대량생산 방식에는 접합하지 않아, 연구용, 특수목적용 등에 적용이 되며 초격자구조,

양자점 구조 등 복합한 구조에 적합 합니다.

그림 MBE 개략도

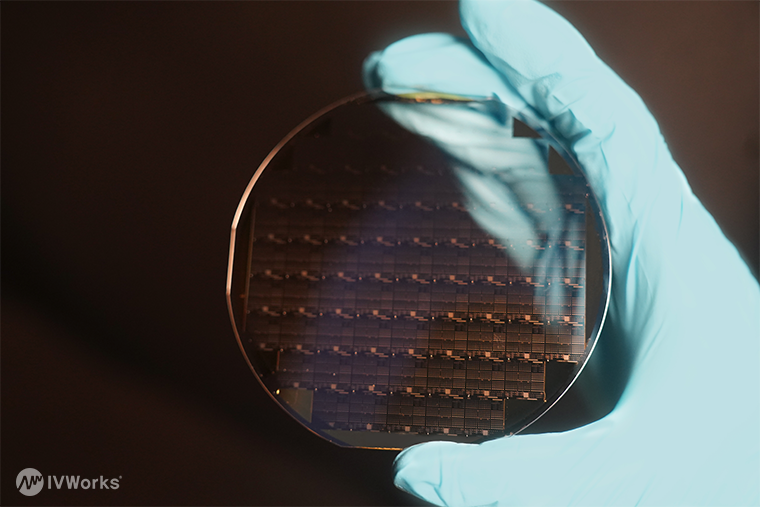

Epitaxy 공정이 끝나면 아래 와 같은 형태의 GaN Epiwafer 웨이퍼가 나오게 됩니다.

격자 패턴을 육안으로 확인할 수 있습니다.

사진 N+-GaN Regrowth epiwafe (출처 : 아이브웍스)

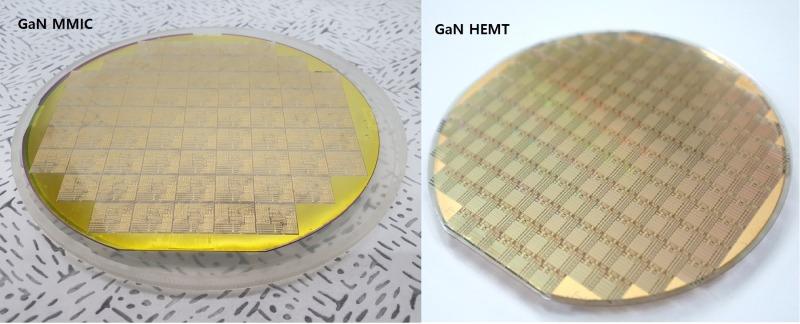

아래는 GaN Epiwafer 전문회사로부터 주문 제작한 Epiwafer를 이후 고객사 공정을 거쳐 나온

형태의 예시 입니다.

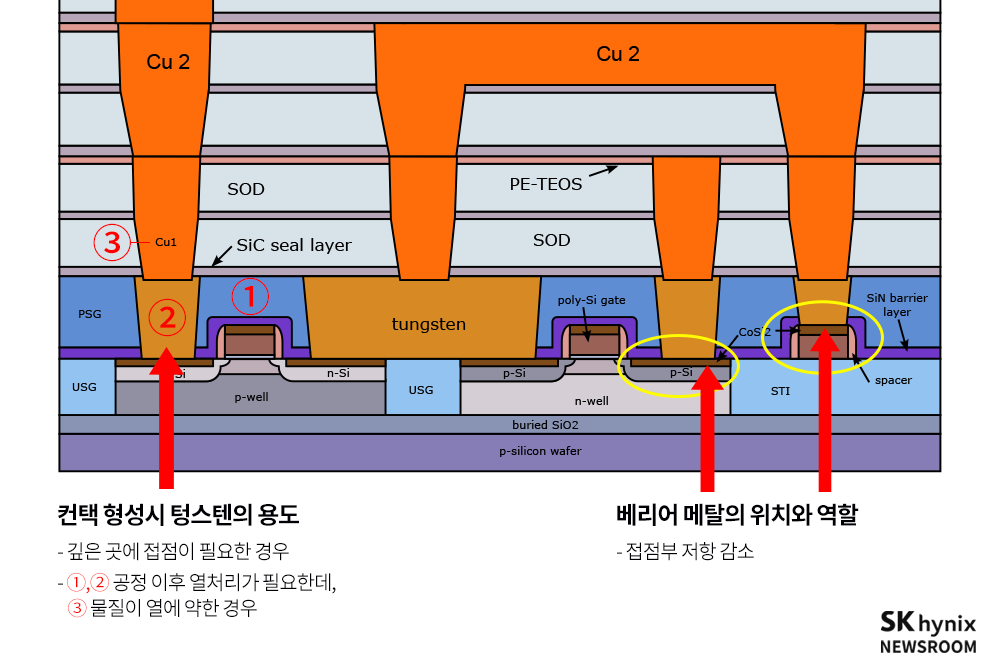

3. 금속 배선 공정

Epi Wafer를 산화,포토,식각,증착 공정을 거치고 나면 Wafer 위에 형성 된 능동,수동 소자등

으로 이루어진 회로가 형성이 됩니다.

이 회로가 동작하기 위해서는 외부에서 전기적 신호를 가해주어야 하는데요.

신호가 잘 전달되도록 반도체 회로 패턴에 따라 전기길(금속선)을 연결하는 작업을

금속배선 공정이라고 합니다.

보통 기판 의 소자들을 연결할 때는 전선을 연결한 뒤 납땜 합니다만,

반도체의 경우, 아래에서 위로 쌓아 올리는 방식을 사용하기 때문에,

하부의 소자층을 형성한 다음, 그 위에 컨택이라고 부르는 소자와 금속배선의 연결부를 만들고

그 위에 금속배선을 연결 합니다.

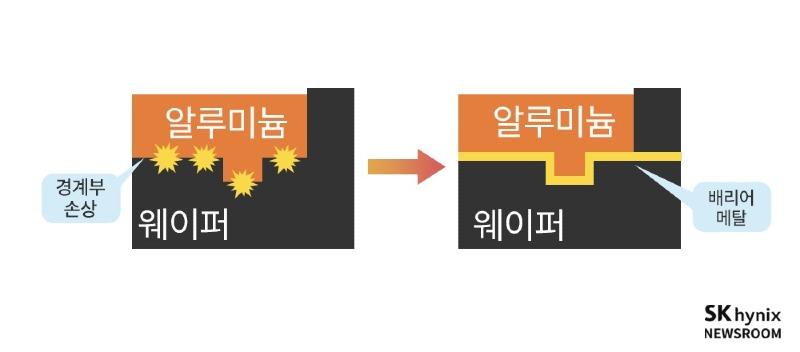

소자와 접점 사이에는 배리어 메탈(Barrier metal)이라는 금속(혹은 금속 화합물)이

필요 합니다.

반도체 공정에서 금속이 아닌 물질과 금속인 물질을 정확하게 접합하기는 매우 어려운 일이며,

특성이 다른 두 물질이 바로 접합되면 그 경계에서 큰 저항이 발생 하게 됩니다.

이는 반도체의 전력 소모를 증가 시킵니다.

이를 막기 위해서 경계면이 ‘자연스럽게’ 비금속에서 금속으로 변하는 것처럼 만들어야 하는데,

여기에 배리어 메탈이 사용 됩니다.

배리어 메탈을 만들기 위해선 반도체 소자의 규소층 위에 티타늄(Ti)이나 코발트(Co)와 같은

층을 올려주면, 이 금속들이 규소 원자와 반응시키면 된다.

이런 과정을 Silicidation이라 부르며, 해당 부위를 Contact Silicide라 부릅니다.

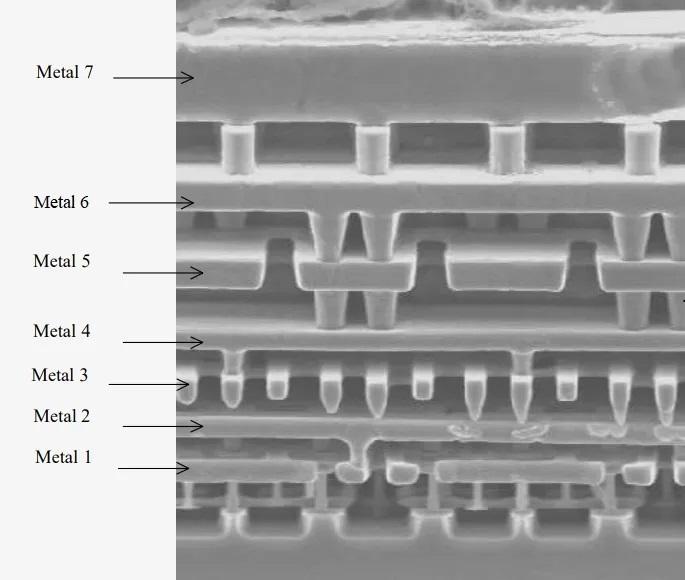

금속 배선 공정은 흔히 생각 하는 얇은 선으로 잇는게 아니라,

화학적 기상증착 방법(CVD)을 통해 금속 배선 공정이 이루어 지게 됩니다.

금속배선까지 끝난 반도체의 단면은 아래와 같습니다.

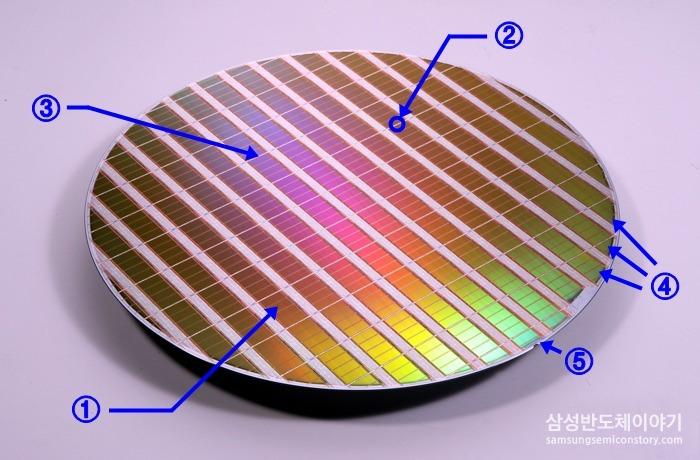

그리고 금속 배선 까지 끝난 웨이퍼의 모양이 우리가 흔히 알고 있는 반도체 웨이퍼 입니다.

가끔 GaN 반도체 국산화 뉴스에서 많이 보던 웨이퍼 들이죠.....ㅎㅎ

아래는 웨이퍼의 각부 명칭 입니다.

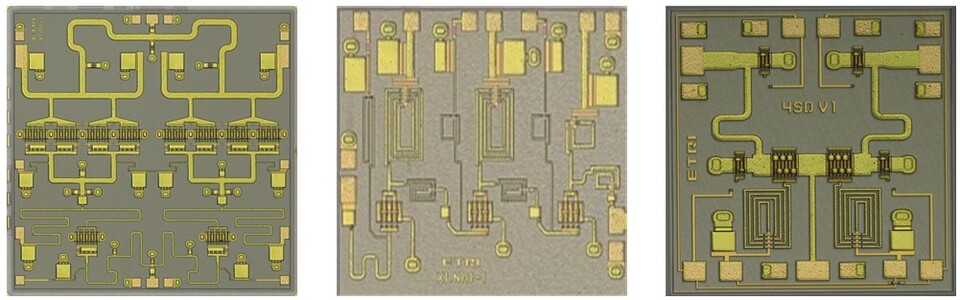

a. X-대역 GaN 전력증폭기 집적회로 칩(왼쪽),

b. X-대역 GaN 저잡음증폭기 집적회로 칩(가운데),

c. X-대역 GaN 스위치 집적회로 칩(오른쪽)

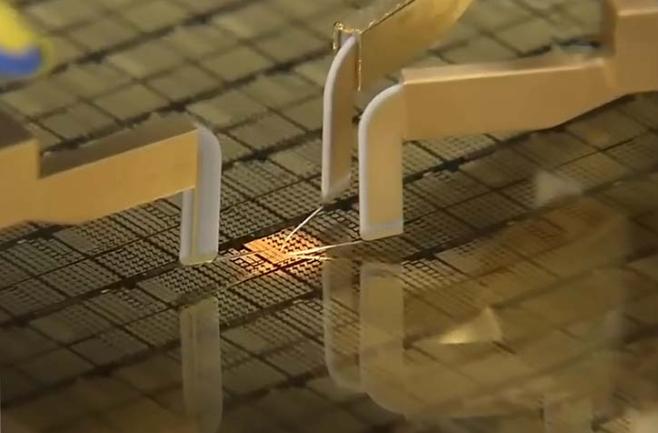

4.EDS(Electrical Die Sorting)

금속 배선이 끝난 웨이퍼는 EDS(Electrical Die Sorting) TEST를 수행하여,

전기적 특성검사를 통해 웨이퍼 상태인 각각의 칩들이 원하는 품질 수준에

도달하는 지를 체크하여, 양품 과 불량을 걸러냅니다.

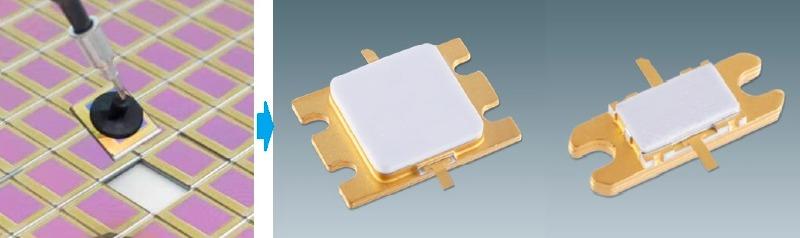

이후 EDS 테스트가 끝난 웨이퍼는 8.패키징공정을 통해 드디어 소자 또는 Chip 형태의 상품으로써

태어나게 됩니다.

지금 까지 긴글 읽어 주시냐고 감사 합니다.

아무래도 비전문가의 글이 다보니 많이 미흡 하고, 경우 따라 잘못 된 정보가 있을수 있습니다.

이점에 대해서는 양해 부탁 드립니다.

여기 까지 잘 읽으셨다면, 이후 GaN 소자 또는 국산 AESA 레이더 핵심부품 국산화 등

이야기 나오면, 왠만하면 다 저게 어떤거지 ,뭐 하는건지 등 이해가 되실 껍니다.